## Abnormal oscillation prevention in overtone oscillation circuit

- Check that overtone oscillation is applied to the applicable crystal. (See the note below.)

- 2 Confirm that the crystal supplier has checked that a difference of 3 dB MIN between primary oscillation and sub-oscillation levels is satisfied in its manufacturing process.

- ③ Confirm that the crystal supplier has described the following in the delivery specifications issued by the supplier: "A difference of 3 dB MIN between the primary and sub-oscillation levels of crystal oscillator is guaranteed in the control unit operating temperature range."

Reference value

Fhe following relationship must be satisfied in the control unit operating temperature range: (Primary oscillation level) - (sub-oscillation level) > 3 dB

Key

-xplanation

E2-A

2

Confirm that an agreement on the sub-oscillation level has been made between the control unit supplier and the crystal supplier at the development stage.

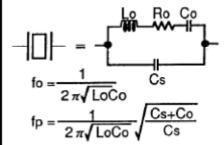

Fig. a shows a general overtone oscillation circuit (Colpitts type). It is necessary in the overtone oscillation circuit to determine a constant so that the frequency characteristic fa of the tank (LC resonance) circuit consisting of La and Ca is the capacitive reactance in the applicable oscillation frequency, in order to obtain the higher-harmonic order frequency (tertiary order in Figures a and b). To obtain tertiary harmonic oscillation, for an instance, fa must be set at the center between the fundamental wave fo and the frequency 3fo being three times higher than fo, as shown in Fig. b.

When the crystal oscillator is oscillated in overtone mode (tertiary, quinary, etc.) even if the oscillator was originally made for thicker slip vibration, some other oscillation modes such as border vibrations are also detected. As might be expected, the vibration frequency of those modes is different from that of the intended mode (primary vibration), which is called the suboscillation, or spurious vibration (frequency). Generally, the sub-oscillation is not generated when a difference between the primary and sub-oscillation levels is 2 dB MIN. So, 3 dB MIN is used as the reference value by the crystal supplier.

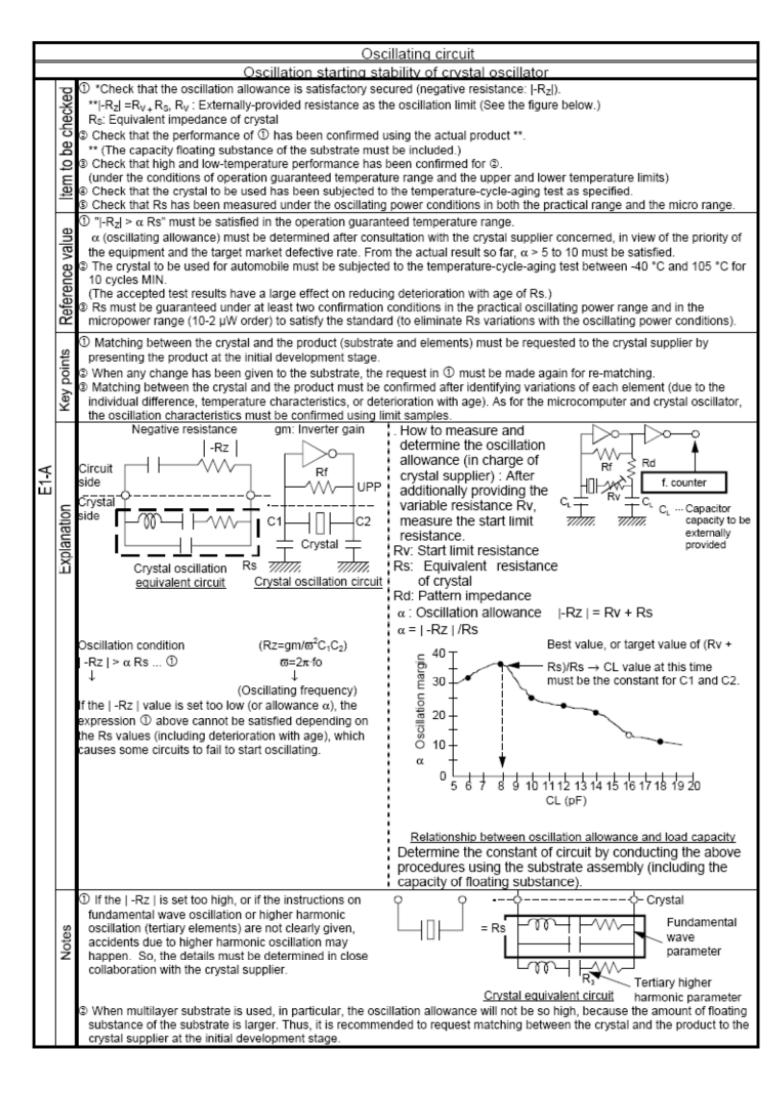

Fig. c shows an example of measured data in which the difference between the primary and sub-oscillation levels is 3.84 dB, satisfying the reference value.

Positive reactance IC side 3fo Tank circuit La 5fo eactance. Negative Ca

Fig a: Basic configuration of evertone oscillation circuit

Fig. b: Frequency characteristics of tank Fig. c: An example of measurement of

primary and sub-oscillation levels

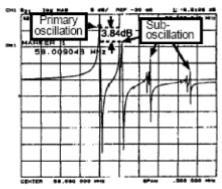

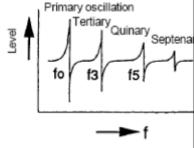

A crystal oscillator is shown as an equivalent circuit as in Fig. d, showing an inductive reactance between the series resonance frequency (fo) and the parallel resonance frequency (fp) as in Fig. e, and oscillates in this frequency range. lowever, the crystal oscillator also has resonance points at the frequency being three times or five times higher than fo as in ig. f, showing the inductive reactance. It is thus possible to generate oscillation in the frequency ranges of f3 and f5 as well by providing the circuit with the capacitive reactance characteristics in these frequency ranges. This is called overtone oscillation

Fig. d: Crystal oscillator equivalent circuit

Fig. e: Reactance frequency characteristics of crystal oscillator

Fig. f: Overtone oscillation vibration level

## Oscillating stability of ceramic oscillator onfirm the following items with an actual product. The oscillation characteristics (oscillating level, oscillation starting voltage, and oscillation rise time) must be confirmed in consideration of the variations of each element (due to individual difference, temperature characteristics, and deterioration with age). checked Check that the characteristics of ceramic oscillator (Ro and Ra) and microcomputer/IC (gain) have been confirmed with limit samples. Check that the oscillation characteristics have been confirmed at high and low temperatures (in the operating guaranteed temperature range, and between the upper and lower limit temperatures). 3The oscillation allowance in Item E1-A above must be confirmed by the negative resistance method. pe The open loop characteristics must be confirmed in consideration of the variations of the oscillation wave and spurious wave. The measuring conditions such as input voltage and applied impedance must be described. Also the temperature characteristics of 2 elements confirmed at normal temperature must be considered. tem Check that the loop gain allowance has been satisfactorily secured. (Loop gain with oscillation frequency; fosc = phase 0°; See Fig. 3 in the explanation column below). Check that the loop phase allowance has been satisfactorily secured. (Loop phase amount with gain 0 dB: See Fig. 3 in the explanation column.) Check that the loop gain difference between the oscillation wave and spurious wave has been satisfactorily secured. The oscillation level (clock X<sub>out</sub>-grounding, X<sub>e</sub>-grounding amplitude) must exceed the HIGH-level minimum standard and the LOW-level maximum standard values for input and output of the microcomputer (IC), under the conditions of operation-guaranteed voltage and g temperature ranges in consideration of variations of the oscillation circuit elements. Also, any symptom of abnormal oscillation\* must not exist at oscillation starting. \* Generation of spurious elements Reference Negative resistance method I -Rz I > α Rs, α (Oscillation allowance) > 3 to 5 shall be met. 3-1 Loop gain allowance target ... 5dB (Worst sample) ~ 10dB (Type sample) MIN 3-2 Loop phase allowance target ... I -20 | deq (Worst sample) ~ | -40 | deq (Type sample)MIN S-3 The loop gain of the oscillation frequency must be higher by 5 dB MIN than that of the spurious frequency (tertiary and quinary overtone elements). It is perfectly acceptable when the spurious gain is 0 dB MAX. Matching between the ceramic oscillator and the product (the microcomputer and the ECU substrate) must be requested to the oscillator points supplier by presenting the product. When any change in the substrate has been given, matching confirmation must be requested again. ě When a lower frequency value is selected in the microcomputer which has an oscillation-frequency selective function, the spurious oscillation will easily occur due to surplus loop gain. So, this must be carefully studied in matching confirmation. Resonant frequency Ro and Ra have a OLoop gain G • α . β≥ 1 Gain allowance 5 ~10 dB correlation that The loop gain must be 0 dB MIN at fosc Trade-off of ceramic oscillator the higher one Amount of phase shift 8 = 81 + 82 = 360° Xn Phase allowance relation Antiresonant becomes, the frequency lower the other Ro-Fr<fosc<Fa becomes. fosc = $1/2 \pi \sqrt{[L1 C_1 (C_0 CL) / (C_0 C_1 + CL)]}$ Fa When Ro is reduced, Frequency (MHz) CL1, CL2 Oscillation frequency However, CL = CL1CL2 / (CL1+CL2) the gain will increase smal C1 Ro L1 Explanation Gain When CL1 and CL2 Amplification (dB) 000 41 w. allowance factor are increased, the 401 gain will decrease. nie B doo-Co CL1, CL2 Fig. 1: Ceramic oeclilator equivalent circuit large Ampitfier CL1, CL2 When Ra is + 180° small reduced, the \*2: 0 1 phase pplication rotation will be Feedback IC Input worsened. circuit 01 Rd≤ Xout (Phase Rd Gain restricting Phase allowance °2: 02 fosc2 CL1, CL2 When CL1 and CL2 are resistance CL1, CL2 and Rd large increased, the phase rotation will be improved. CL<sub>2</sub> must be adjusted for - 180° Fig. 2: Outline of gain and phase measurement for open loop characteristics of oscillation circuit Fig. 3: Relation between gain/phase characteristics of oscillation circuit and effect factors C1 R<sub>0</sub> The phase rotation of the ceramic oscillators is relatively worse than that of the 000 Fundamental. crystal oscillators, because the antiresonant resistance Ra is smaller. If the gain is ٦ <u>۴</u> wave set too high in matching confirmation, the phase will be reduced too much, parameter generating the spurious oscillation (tertiary and quinary elements) easily. To 15551 - H-,VV Notes しょうシーコ トーシャペー prevent this problem, it is important to keep a balance between the gain allowance and the phase allowance, and to reduce the gain of the spurious wave \*1: Spurious wave with tertiary element \*2: Spurious wave with quinary element substantially in comparison with that of the oscillation wave. Oscillation stability conditions Matching confirmation conditions in consideration of variations Microcomputer Microcom-Rο Ra Ro Ra C11, C12 puter gain gain Min Gain Gain max tolerance Small Large Small product Fundamen-Fundamen product allowane max tal wave tal wave Phase min Phase tolerance oscillation oscillation Large Large allowanc allowance product min tolerance Max Spurious oscillation Spurious oscillation max min High Low High Low product product . esistance product resistance min

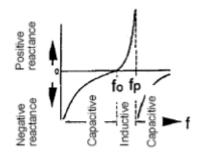

Oscillating circuit